## Simulink<sup>®</sup> Design Verifier™ Reference

# MATLAB&SIMULINK®

**R**2019**b**

### **How to Contact MathWorks**

Latest news: www.mathworks.com Sales and services: www.mathworks.com/sales\_and\_services User community: www.mathworks.com/matlabcentral Technical support: www.mathworks.com/support/contact\_us Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick. MA 01760-2098

Simulink<sup>®</sup> Design Verifier<sup>™</sup> Reference

© COPYRIGHT 2007-2019 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### Trademarks

Prover, Prover Technology, Prover Plug-In, and the Prover logo are trademarks or registered trademarks of Prover Technology AB in Sweden, the United States, and in other countries. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See <a href="http://www.mathworks.com/trademarks">www.mathworks.com/trademarks</a> for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

10

#### **Revision History**

| •                                                                              |                                                          |

|--------------------------------------------------------------------------------|----------------------------------------------------------|

| September 2010<br>April 2011<br>September 2011<br>March 2012<br>September 2012 | Online only<br>Online only<br>Online only<br>Online only |

| March 2013                                                                     | Online only                                              |

| September 2013                                                                 | Online only                                              |

| March 2014                                                                     | Online only                                              |

| October 2014                                                                   | Online only                                              |

| March 2015                                                                     | Online only                                              |

| September 2015                                                                 | Online only                                              |

| October 2015                                                                   | Online only                                              |

| March 2016                                                                     | Online only                                              |

| September 2016                                                                 | Online only                                              |

| March 2017                                                                     | Online only                                              |

| September 2017                                                                 | Online only                                              |

| March 2018                                                                     | Online only                                              |

| September 2018                                                                 | Online only                                              |

| March 2019                                                                     | Online only                                              |

| September 2019                                                                 | Online only                                              |

|                                                                                |                                                          |

New for Version 1.7 (Release 2010b) Revised for Version 2.0 (Release 2011a) Revised for Version 2.1 (Release 2011b) Revised for Version 2.2 (Release 2012a) Revised for Version 2.3 (Release 2012b) Revised for Version 2.4 (Release 2013a) Revised for Version 2.5 (Release 2013b) Revised for Version 2.6 (Release 2014a) Revised for Version 2.7 (Release 2014b) Revised for Version 2.8 (Release 2015a) Revised for Version 3.0 (Release 2015b) Rereleased for Version 2.8.1 (Release 2015aSP1) Revised for Version 3.1 (Release 2016a) Revised for Version 3.2 (Release 2016b) Revised for Version 3.3 (Release 2017a) Revised for Version 3.4 (Release 2017b) Revised for Version 3.5 (Release 2018a) Revised for Version 4.0 (Release 2018b) Revised for Version 4.1 (Release 2019a) Revised for Version 4.2 (Release 2019b)

# Contents

#### **Functions – Alphabetical List**

#### **Blocks – Alphabetical List**

#### **Model Advisor Checks**

#### Simulink Design Verifier Checks 3-2 Simulink Design Verifier Checks Overview ..... 3-2Check compatibility with Simulink Design Verifier ..... 3-2 Detect Dead Logic 3-4 Detect Out Of Bound Array Access 3-6 Detect Division by Zero 3-7 Detect Integer Overflow 3-8 Detect Non-finite and NaN Floating-Point Values ..... 3-10 Detect Subnormal Floating-Point Values ..... 3-11 Detect Specified Minimum and Maximum Value Violations . . 3-12 Detect Data Store Access Violations 3-14

1

2

3

# **Functions — Alphabetical List**

### sldv.assume

Proof assumption function for Stateflow charts and MATLAB Function blocks

### Syntax

sldv.assume(expr)

### Description

sldv.assume(expr) specifies that expr is true for every evaluation while proving

properties. Use any valid Boolean expression for expr.

This function has no output and no impact on its parenting function, other than any indirect side effects of evaluating expr. If you issue this function from the MATLAB<sup>®</sup> command line, the function has no effect.

Intersperse sldv.assume proof assumptions within MATLAB code or separate the assumptions into a verification script.

The **Proof assumptions** option in the **Property proving** pane applies to the proof assumptions represented by the sldv.assume function and by the Proof Assumption block.

### Examples

#### **Specify Property Proof Objective and Proof Assumption**

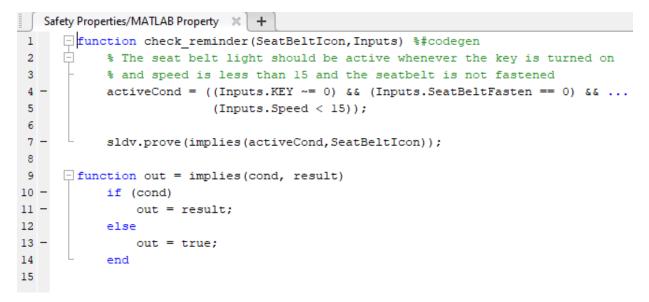

Specify a property proof objective and proof assumption in the sldvdemo\_sbr\_verification model by using a MATLAB Function block.

Open the sldvdemo\_sbr\_verification model and save it as ex\_sldvdemo\_sbr\_verification.

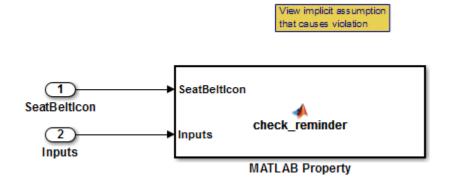

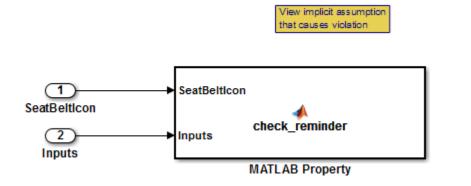

Open the Safety Properties subsystem.

Open the MATLAB Property block, which is a MATLAB Function block.

At the end of the check\_reminder function definition, add sldv.assume(Inputs.KEY==0 | 1); so that the last two lines of the function definition are:

```

sldv.prove(implies(activeCond, SeatBeltIcon));

sldv.assume(Inputs.KEY==0 | 1);

```

To save the updated code, in the Editor tab, click Save and close the editor.

To prove the safety properties, in the Simulink Editor, select the Safety Properties subsystem. On the **Design Verifier** tab, click **Prove Properties**.

Alternatively, in the Simulink Editor, you can right-click the Safety Properties subsystem and select **Design Verifier > Prove Subsystem Properties**.

### **Input Arguments**

expr — Boolean expression for assumption boolean expression

MATLAB expression, for example, x > 0.

### Alternatives

Instead of using the sldv.assume function, you can insert a Proof Assumption block in your model. Using sldv.assume instead of a Proof Assumption block offers several benefits, described in "What Is Property Proving?".

When proving models by using MATLAB for code generation, you can also constrain signal values without using the sldv.assume function. Using sldv.assume instead of directly using MATLAB for code generation eliminates the need to:

- Express the assumption by using a Simulink block.

- Explicitly connect the assumption output to a Simulink block.

### See Also

Proof Assumption | Proof Objective | Test Condition | Test Objective | sldv.condition | sldv.prove | sldv.test

### Topics

"Prove Properties in a Model" "Workflow for Proving Model Properties" Introduced in R2009b

### sldvblockreplacement

Replace blocks for analysis

### Syntax

```

[status,newmodel] = sldvblockreplacement(model)

[status,newmodel] = sldvblockreplacement(model,options)

[status,newmodel] = sldvblockreplacement(model,options,showUI)

sldvblockreplacement(model,options)

```

### Description

[status,newmodel] = sldvblockreplacement(model) copies the model model and replaces specified model blocks and other model components for a Simulink Design Verifier analysis. sldvblockreplacement replaces the blocks of the model according to the block-replacement rules in the model configuration settings.

[status,newmodel] = sldvblockreplacement(model,options) replaces the blocks of the model model according to the block-replacement rules specified in the sldvoptions object options, and returns a handle to the new model in newmodel.

[status,newmodel] = sldvblockreplacement(model,options,showUI)

performs the same tasks as sldvblockreplacement(model,options). If showUI is

true, errors appear in the Diagnostic Viewer. Otherwise, errors appear at the MATLAB

command line.

### **Examples**

#### **Replace Blocks in Model by Using Block-Replacement Rules**

Replace the blocks in sldvdemo\_sqrt\_blockrep model by using the block-replacement rules specified in opts.

Open the sldvdemo\_sqrt\_blockrep example model.

```

open_system('sldvdemo_sqrt_blockrep');

```

Set the sldvoptions and specify the block-replacement rule.

Create a model by using sldvblockreplacement.

```

[status, newmodel] = sldvblockreplacement('sldvdemo_sqrt_blockrep', opts);

```

### **Input Arguments**

#### model - Name or handle of model

character vector | string scalar

Name or handle to a Simulink model.

#### options — Specify analysis parameters

[] (default) | character vector

sldvoptions object that specifies the analysis parameters.

#### showUI — Display messages during analysis

logical

Logical value indicating where to display messages during analysis. true to display diagnostic messages in the Diagnostic Viewer false (default) to display messages in the MATLAB command window

### **Output Arguments**

#### status — Status of block-replacement

logical

If the operation replaces the blocks, sldvblockreplacement returns a status of 1. Otherwise, it returns 0.

#### newmodel - Handle to new model

double

sldvblockreplacement returns a handle to the new model in newmodel.

### See Also

sldvoptions

### Topics

"Block Replacements for Unsupported Blocks"

#### Introduced in R2007a

### sldvcompat

Check model for compatibility with analysis

### **Syntax**

```

status = sldvcompat(model)

status = sldvcompat(subsystem)

status = sldvcompat(subsystem, options)

status = sldvcompat(model, options, showUI, startCov)

```

### Description

status = sldvcompat(model) returns a status of 1 if the model is compatible with Simulink Design Verifier software. Otherwise, sldvcompat returns 0.

status = sldvcompat(subsystem) converts the Simulink atomic subsystem

subsystem into a temporary model and checks the compatibility of the temporary model

with Simulink Design Verifier software. After the compatibility check, sldvcompat closes

the temporary model.

status = sldvcompat(subsystem, options) checks the subsystem specified by subsystem for compatibility with Simulink Design Verifier software by using the sldvoptions object options.

status = sldvcompat(model, options, showUI, startCov) checks the compatibility of the model with Simulink Design Verifier software. If showUI is true, errors appear in the Diagnostic Viewer. Otherwise, errors appear at the MATLAB command line. The analysis ignores all model coverage objectives satisfied in startCov, a cvdata object.

### **Examples**

#### **Check Model Compatibility**

Check the sldvdemo\_flipflop model for compatibility with Simulink Design Verifier software.

Open the sldvdemo\_flipflop example model and check for compatibility.

```

open_system('sldvdemo_flipflop');

status = sldvcompat('sldvdemo_flipflop');

```

### **Input Arguments**

#### model - Handle to model

[] (default) | character vector | string scalar

#### Handle to a Simulink model.

Example: 'sldvdemo\_flipflop'

#### subsystem — Handle to atomic subsystem

character vector | string scalar

Handle to an atomic subsystem in a Simulink model.

#### options — Analysis parameters

[] (default) | character vector | string scalar

sldvoptions object that specifies the analysis parameters.

#### showUI — Display messages during analysis

logical

Logical value indicating where to display messages during analysis: true to display messages in the log window. false (default) to display messages in the Command Window.

#### startCov — Coverage data for model

character vector | string scalar

A cvdata object that contains coverage data for the model.

### **Output Arguments**

#### status — Model is compatible

logical

If the model is compatible with Simulink Design Verifier software, the status is 1 . Otherwise, sldvcompat returns 0.

### Alternatives

To check if a model is compatible with Simulink Design Verifier, on the **Design Verifier** tab, in the **Analyze** section, click **Check Compatibility**.

To check the compatibility of a subsystem, right-click the subsystem and select **Design Verifier > Check Subsystem Compatibility**.

### See Also

sldvoptions|sldvrun

### Topics

"Check Compatibility of the Example Model"

#### Introduced in R2007a

### sldv.condition

Test condition function for Stateflow charts and MATLAB Function blocks

### Syntax

```

sldv.condition(expr)

```

### Description

sldv.condition(expr) specifies that expr is true for every time step in a generated

test case. Use any valid Boolean expression for expr.

This function has no output and no impact on its parenting function, other than any indirect side effects of evaluating expr. If you issue this function from the MATLAB command line, the function has no effect.

Intersperse sldv.condition test conditions within MATLAB code or separate the conditions into a verification script.

The **Test conditions** option in the **Test generation** pane applies to test conditions represented with the sldv.condition function and with the Test Condition block.

### **Examples**

#### Add Test Objective and Test Conditions

Add a test objective and test conditions by using the MATLAB Function block.

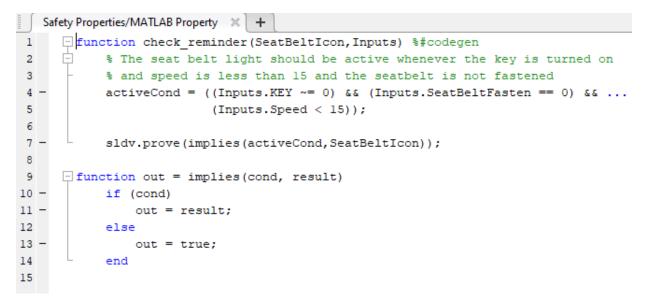

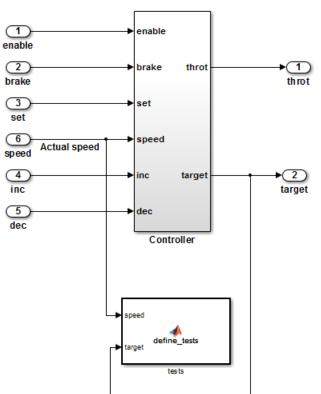

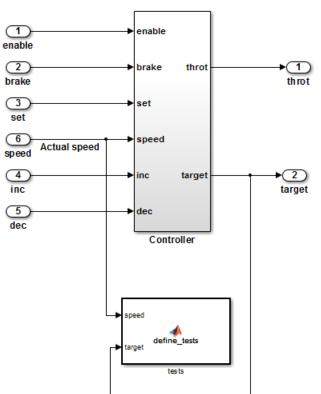

Open the sldvdemo\_cruise\_control model and save it as ex\_sldvdemo\_cruise\_control.

Remove the Test Condition block for the **speed** block signal. Instead of the Test Condition block, this example uses **sldv.test** and **sldv.condition**.

From the User-Defined Functions library, add a MATLAB Function block:

- **1** Name the block tests.

- **2** Open the block and add this code:

```

function define_tests(speed, target)

%#codegen

```

```

sldv.condition(speed >= 0 && speed <= 100);

sldv.test(speed > 60 && target > 40 && target < 50);

sldv.test(speed < 20 && target > 50);

```

- 3 In the **Editor** tab, click **Save** and close the editor.

- 4 Connect the block to the signals for the speed block and for the target block.

Save the changes to the ex\_environment\_controller model.

Simulink Design Verifier Cruise Control Test Generation

To generate test cases, on the **Design Verifier** tab, click **Generate Tests**.

### **Input Arguments**

#### expr — Boolean expression for condition

boolean expression

MATLAB expression, for example, x > 0.

### Alternatives

Instead of using the sldv.condition function, you can insert a Test Condition block in your model. Using sldv.condition instead of a Test Condition block offers several benefits, described in "What Is Test Case Generation?".

You can also specify test conditions by using MATLAB for code generation without using the sldv.condition function. Using sldv.condition instead of directly using MATLAB for code generation eliminates the need to:

- Express the constraints with Simulink blocks.

- Explicitly connect the condition output to a Simulink block.

### See Also

Proof Assumption | Proof Objective | Test Condition | Test Objective | sldv.assume | sldv.prove | sldv.test

### **Topics**

"Generate Test Cases for Model Decision Coverage" "Workflow for Test Case Generation"

#### Introduced in R2009b

### sldvextract

Extract subsystem or subchart contents into new model for analysis

### Syntax

```

newModel = sldvextract(subsystem)

newModel = sldvextract(subchart)

newModel = sldvextract(exportfcnmodel)

newModel = sldvextract(subsystem, showModel)

newModel = sldvextract(subchart, showModel)

```

### Description

newModel = sldvextract(subsystem) extracts the contents of the atomic subsystem subsystem and creates a model for the Simulink Design Verifier software to analyze. sldvextract returns the name of the new model in newModel. If the model name exists, sldvextract uses the subsystem name for the model name, appending a number to the model name.

newModel = sldvextract(subchart) extracts the contents of the atomic subchart subchart and creates a model for the Simulink Design Verifier software to analyze. Specify the full path of the atomic subchart in subchart. If the model name exists, sldvextract uses the subchart name for the model name, appending a number to the model name.

**Note** If the atomic subchart calls an exported graphical function that is outside the subchart, sldvextract creates the model, but the new model will not compile.

newModel = sldvextract(exportfcnmodel) creates a scheduler model that invokes the export-function model exportfcnmodel for analysis by Simulink Design Verifier. sldvextract returns the name of the new model in newModel. The newModel consists of exportfcnmodel model name with a suffix SldvScheduler. If the model name already exists, sldvextract uses the exportfcnmodel name for the model name, appending a number to the model name.

```

newModel = sldvextract(subsystem, showModel) and newModel =

sldvextract(subchart, showModel) opens the extracted model when you set

showModel to true. If showModel is set to false, the extracted model is only loaded

into workspace.

```

### **Examples**

#### **Extract the Atomic Subsystem**

Extract the atomic subsystem Bus Counter from the sldemo\_mdlref\_conversion model and copy it to a new model.

```

open_system('sldemo_mdlref_conversion');

newmodel = sldvextract('sldemo_mdlref_conversion/Bus Counter', true);

```

#### **Extract the Atomic Subchart**

Extract the atomic subchart, Sensor1, from the sf\_atomic\_sensor\_pair model and copy it to a new model.

```

open_system('sf_atomic_sensor_pair');

newmodel = sldvextract('sf_atomic_sensor_pair/RedundantSensors/Sensor1',...

true);

```

#### **Create the Scheduler for Export-Function Model**

Create the scheduler model that invokes the sldvExportFunction\_autosar\_multirunnables model.

```

open_system('sldvExportFunction_autosar_multirunnables');

newmodel = sldvextract('sldvExportFunction_autosar_multirunnables');

```

### **Input Arguments**

#### subsystem — Path to atomic subsystem

character vector | string scalar

Full path to the atomic subsystem.

#### subchart — Path to Stateflow atomic subchart

character vector | string scalar

Full path to the Stateflow<sup>®</sup> atomic subchart.

exportfcnmodel — Path to export-function model

character vector | string scalar

Full path to the export-function model.

showModel — Display the extracted model

True (default) | logical

Logical value that indicates whether to display the extracted model.

### **Output Arguments**

**newModel** — **Name of new model** character vector

Name of the new model.

### See Also

### **Topics**

"Extract Subsystems for Analysis" "Analyze Export-Function Models"

Introduced in R2007a

### sldvgencov

Analyze models to obtain missing model coverage

### Syntax

```

[status, cvdo] = sldvgencov(model, options, showUI, startCov)

[status, cvdo] = sldvgencov(block, options, showUI, startCov)

[status, cvdo, filenames] = sldvgencov(model, options, showUI,

startCov)

[status, cvdo, filenames, newmodel] = sldvgencov(block, options,

showUI, startCov)

```

### Description

[status, cvdo] = sldvgencov(model, options, showUI, startCov) analyzes the model model by using the sldvoptions object options.

[status, cvdo] = sldvgencov(block, options, showUI, startCov) analyzes the atomic subsystem block by using the sldvoptions object options.

```

[status, cvdo, filenames] = sldvgencov(model, options, showUI,

startCov) analyzes the model and returns the file names that the software creates in

filenames.

```

```

[status, cvdo, filenames, newmodel] = sldvgencov(block, options,

showUI, startCov) analyzes the block by using the sldvoptions object options.

The software returns a handle to the newmodel, which contains a copy of the block

subsystem.

```

### Examples

#### **Collect Missing Coverage Data**

Analyze the coverage data and collect the missing coverage data.

Analyze the Cruise Control model and simulate a version of that model by using data from test cases from the previous analysis. Compare the model coverage data and collect the coverage missing from the sldvdemo\_cruise\_control\_mod model analysis:

```

opts = sldvoptions;

% Generate test cases

opts.Mode = 'TestGeneration';

% Specify MCDC coverage

opts.ModelCoverageObjectives = 'MCDC';

% Don't create harness model

opts.SaveHarnessModel = 'off';

% or report

opts.SaveReport = 'off';

open system 'sldvdemo cruise control';

[ status, files ] = sldvrun('sldvdemo cruise control', opts);

open system 'sldvdemo cruise control mod';

[ outData, startCov ] = sldvruntest('sldvdemo cruise control mod',...

files.DataFile, [], true);

cvhtml('Coverage with the original test suite', startCov);

[ status, covData, files ] = sldvgencov('sldvdemo cruise control mod',...

opts, false, startCov);

```

### **Input Arguments**

#### block — Handle to an atomic subsystem

character vector | string scalar

Handle to an atomic subsystem in a Simulink model.

#### model - Handle to a model

[] (default) | character vector | string scalar

Handle to a Simulink model.

#### options — Analysis parameters

[] (default) | character vector | string scalar

sldvoptions object that specifies the analysis parameters.

#### showUI — Display messages during analysis

logical

Logical value that indicates where to display messages during analysis: true to display messages in the log window. false (default) to display messages in the MATLAB command window.

#### startCov — Model coverage data

[] (default) | character vector | string scalar

${\tt cvdata}$  object. The analysis ignores model coverage objectives already satisfied in  ${\tt startCov}.$

### **Output Arguments**

cvdo — Coverage data character vector

cvdata object containing coverage data for new tests.

#### filenames — Analysis results file names

structure

A structure whose fields list the file names resulting from the analysis.

| DataFile              | MAT-file with the raw input data.                 |

|-----------------------|---------------------------------------------------|

| HarnessModel          | Simulink harness model.                           |

| Report                | HTML report of the results.                       |

| ExtractedModel        | Simulink model extracted from the subsystem.      |

| BlockReplacementModel | Simulink model obtained after block replacements. |

#### status — Status of model coverage data

logical

Logical value that indicates if the analysis collected model coverage. true for analysis collected model coverage data. false if analysis does not collect model coverage data.

### See Also

sldvmergeharness|sldvoptions|sldvrun|sldvruntest

**Topics** "Generate Test Cases for Model Decision Coverage"

Introduced in R2007a

### sldvharnessopts

Default options for sldvmakeharness

### Syntax

harnessopts = sldvharnessopts

### Description

harnessopts = sldvharnessopts generates the default configuration for running sldvmakeharness.

### **Examples**

#### **Create Test Harness Model by Using Default Options**

Create a test harness for the sldvdemo\_cruise\_control model by using the default options.

Open the sldvdemo\_cruise\_control example model.

open\_system('sldvdemo\_cruise\_control');

Using the default options, create a test harness for the sldvdemo\_cruise\_control model.

```

harnessOpts = sldvharnessopts;

[harnessfile] = sldvmakeharness('sldvdemo_cruise_control',...

'', harnessOpts);

```

### **Output Arguments**

#### harnessopts — Options for harness model

structure

A structure whose fields specify the default options for sldvmakeharness when creating a Simulink Design Verifier harness model.

The harnessopts structure can have these fields. If you do not specify values, the configuration uses default values.

| Field           | Description                                                                                                                                                                                                                                                                                                                                            |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| harnessFilePath | Specifies the file path for creating the<br>harness model. If an invalid path is<br>specified, sldvmakeharness does not save<br>the harness model, but it creates and opens<br>the harness model. If you do not specify this<br>option, sldvmakeharness generates a<br>new harness model and saves it in the<br>MATLAB current folder.<br>Default: ' ' |

| modelRefHarness | Generates the test harness model that<br>includes the model in a Model block. When<br>false, the test harness model includes a<br>copy of the model.<br>Default: true                                                                                                                                                                                  |

| Field           | Description                                                                                                                                                                                                                    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| usedSignalsOnly | When true, the Signal Builder block in the<br>harness model has signals only for input<br>signals in the model. Model must be<br>compatible with the Simulink Design<br>Verifier software to detect those input<br>signals.    |

|                 | When the harnessSource parameter is set<br>to Signal Editor, the Signal Editor block<br>in the harness model consists of unused bus<br>signals in addition to the input signals in<br>the model.<br>Default: false             |

| harnessSource   | When set to Signal Builder, Simulink<br>Design Verifier generates a harness model<br>with the Signal Builder block as the Inputs<br>block.<br>When set to Signal Editor, Simulink<br>Design Verifier generates a harness model |

|                 | with the Signal Editor block as the Inputs<br>block.<br>Default: Signal Builder                                                                                                                                                |

### See Also

sldvmakeharness

### Topics

"Simulink Design Verifier Harness Models" "Create Harness Model" "Generate Test Harness Model and Record Coverage Data"

#### Introduced in R2010b

### sldvhighlight

Highlight model using data from Simulink Design Verifier analysis

### Syntax

```

sldvhighlight

sldvhighlight(model)

sldvhighlight(model, dataFile)

sldvhighlight(model, dataFile, Filter)

```

### Description

sldvhighlight highlights the current model by using its active Simulink Design Verifier analysis results. If there are no active results, sldvhighlight loads the latest analysis results for the current model, and then highlights the model by using these results.

sldvhighlight(model) highlights model by using its active Simulink Design Verifier

analysis results. If there are no active results, sldvhighlight loads the latest analysis

results for the model, and then highlights the model by using these results.

sldvhighlight(model, dataFile) loads the Simulink Design Verifier analysis results

from dataFile. The function highlights model by using these results.

sldvhighlight(model, dataFile, Filter) loads the Simulink Design Verifier analysis results from dataFile and the analysis filter file Filter. The function highlights model by using these results.

### Examples

#### Highlight Active Analysis Results on Current Model

Highlight the current model that has active Simulink Design Verifier analysis results.

Open the sldvdemo\_debounce\_modelcov example model.

#### open\_system('sldvdemo\_debounce\_modelcov');

#### Using the default settings, run test generation analysis on the example model.

#### status = sldvrun('sldvdemo\_debounce\_modelcov')

```

Checking compatibility for test generation: model 'sldvdemo_debounce_modelcov'

Compiling model...done

Building model representation...done

'sldvdemo_debounce_modelcov' is compatible for test generation with Simulink Design Verifier.

Generating tests using model representation from 15-Mar-2019 13:12:06...

.....

Completed normally.

Generating output files:

Harness model:

pwd\sldv_output\sldvdemo_debounce_modelcov\sldvdemo_debounce_modelcov_harness.slx

Results generation completed.

Data file:

pwd\sldv_output\sldvdemo_debounce_modelcov\sldvdemo_debounce_modelcov_sldvdata.mat

status =

```

```

1

```

Highlight the results of the analysis on the current model, sldvdemo\_debounce\_modelcov.

sldvhighlight

The example model is highlighted with the analysis results.

To view the detailed analysis results for the object in the Results Inspector, click a highlighted object in the model.

#### Highlight Active Analysis Results on Specified Model

Highlight a specified model that has active Simulink Design Verifier analysis results.

Open the sldvdemo debounce modelcov example model.

```

open_system('sldvdemo_debounce_modelcov')

```

#### Using the default settings, run the test generation analysis on the model.

```

status = sldvrun('sldvdemo_debounce_modelcov')

Checking compatibility for test generation: model 'sldvdemo_debounce_modelcov'

Compiling model...done

Building model representation...done

'sldvdemo_debounce_modelcov' is compatible for test generation with Simulink Design Verifier.

Generating tests using model representation from 15-Mar-2019 13:12:06...

Completed normally.

Generating output files:

Harness model:

pwd\sldv_output\sldvdemo_debounce_modelcov\sldvdemo_debounce_modelcov_harness.slx

Results generation completed.

Data file:

pwd\sldv_output\sldvdemo_debounce_modelcov\sldvdemo_debounce_modelcov_sldvdata.mat

status =

1

```

Highlight the results of the analysis on sldvdemo\_debounce\_modelcov model.

sldvhighlight('sldvdemo\_debounce\_modelcov')

The example model is highlighted with the analysis results.

To view the detailed analysis results for the object in the Results Inspector, click a highlighted object in the model.

#### Highlight Analysis Results from Data File on a Model

Highlight a specified model that has Simulink Design Verifier analysis results, loaded from a data file.

Open the sldvdemo\_debounce\_modelcov example model.

open\_system('sldvdemo\_debounce\_modelcov')

Using the default settings, run the test generation analysis on the example model.

#### status = sldvrun('sldvdemo\_debounce\_modelcov')

```

Checking compatibility for test generation: model 'sldvdemo_debounce_modelcov'

Compiling model...done

Building model representation...done

'sldvdemo_debounce_modelcov' is compatible for test generation with Simulink Design Verifier.

Generating tests using model representation from 15-Mar-2019 13:12:06...

.....

Completed normally.

Generating output files:

Harness model:

pwd\sldv_output files:

Results generation completed.

Data file:

pwd\sldv_output\sldvdemo_debounce_modelcov\sldvdemo_debounce_modelcov_sldvdata.mat

status =

```

Close the example model and the harness model that the analysis produced.

```

bdclose('sldvdemo_debounce_modelcov')

bdclose('sldvdemo_debounce_modelcov_harness')

```

Reopen the example model.

open\_system('sldvdemo\_debounce\_modelcov')

Highlight the example model that has analysis results, stored in the data file that the analysis created.

```

sldvhighlight('sldvdemo_debounce_modelcov',[pwd ...

'\sldv_output\sldvdemo_debounce_modelcov\' ...

'sldvdemo_debounce_modelcov_sldvdata.mat'])

```

The Simulink Design Verifier Results Inspector opens. The model is highlighted to show the results of the analysis.

To view the detailed analysis results for the object in the Results Inspector, click highlighted object in the model.

### **Input Arguments**

#### model — Name or handle of model to highlight

character vector | string scalar

Name of the model or handle of the model to highlight.

```

Example: 'sldvdemo_cruise_control'

```

Example: 'sldvdemo\_flipflop'

#### dataFile — Name of analysis data file

character vector | string scalar

Name of Simulink Design Verifier analysis data file.

For more information about analysis data files, see "Simulink Design Verifier Data Files".

Example: 'results.mat'

```

Example: 'sldv_output\sldvdemo_flipflop

\sldvdemo_flipflop_sldvdata.mat'

```

Example: 'sldv\_output\my\_model\my\_model\_sldvdata.mat'

#### Filter — Name of analysis filter file with justification rules

character vector | string scalar

#### Name of the analysis filter file that contains the justification rules.

```

Example: 'sldvdemo_design_error_detection_sldv_filter.cvf'

```

### See Also

sldvloadresults | sldvreport

### Topics

"Highlighted Results on the Model" "Simulink Design Verifier Data Files" Introduced in R2013b

# sldvisactive

Verify updating of a block diagram

# Syntax

```

status = sldvisactive

status = sldvisactive(model)

status = sldvisactive(block)

```

# Description

status = sldvisactive checks if the software is actively translating the current Simulink model. If the software is actively translating the current model, sldvisactive returns 1. Otherwise, it returns 0.

status = sldvisactive(model) checks if the software is actively translating model.

status = sldvisactive(block) checks if the Simulink Design Verifier software is

actively translating the model that contains block block.

sldvisactive customizes the model analysis in the block and model callback functions

or mask initialization.

## **Input Arguments**

#### model - Name or handle of model

character vector | string scalar

Full path name or handle to a Simulink model.

#### block — Name or handle of block

character vector | string scalar

Full path name or handle to a Simulink block.

## **Output Arguments**

#### status — Actively translating model

logical

If the software is actively translating the current model, sldvisactive returns 1. Otherwise, the status is 0.

### See Also

sldvcompat | sldvextract

### Topics

"Basic Workflow for Simulink Design Verifier" "Check Model Compatibility" "Extract Subsystems for Analysis"

#### Introduced in R2009a

# sidvloadresults

Load Simulink Design Verifier analysis results for model

### Syntax

```

status = sldvloadresults(model)

status = sldvloadresults(model, dataFile)

```

### Description

status = sldvloadresults(model) loads the recently generated Simulink Design

Verifier analysis results for model in the Results Summary window. If model is not open,

sldvloadresults opens the model.

To load the results from the data file, on the **Design Verifier** tab, in the **Review Results** section, click **Load Earlier Results** and open the data file. The sldvloadresults loads the result from this specified data file.

status = sldvloadresults(model, dataFile) loads the analysis results for model

from dataFile in the Results Summary window. If model is not open,

sldvloadresults opens the model. The function loads the results from dataFile.

## **Examples**

#### Load Active Results for Specified Model

Load active Simulink Design Verifier analysis results for a specified model.

Open the sldvdemo\_flipflop example model.

open\_system('sldvdemo\_flipflop');

Run the test generation analysis on the example model by using its default settings.

status = sldvrun('sldvdemo\_flipflop')

```

Checking compatibility for test generation: model 'sldvdemo_flipflop'

Compiling model...done

Building model representation...done

'sldvdemo_flipflop' is compatible for test generation with Simulink Design Verifier.

Generating tests using model representation from 14-Dec-2018 16:33:34...

....

Completed normally.

Generating output files:

Results generation completed.

Data file:

H:\work\sldv_output\sldvdemo_flipflop\sldvdemo_flipflop_sldvdata.mat

status =

1

```

Close the example model.

bdclose('sldvdemo\_flipflop')

Reopen the example model. Load the recently generated analysis results.

```

sldvloadresults('sldvdemo_flipflop')

ans =

1

```

You can view the loaded analysis results in the Simulink Design Verifier Results Summary window. To open the Results Summary window, on the **Design Verifier** tab, in the **Review Results** section, click **Results Summary**.

#### Load Results from Data File for Specified Model

Load Simulink Design Verifier analysis results from data file for a specified model.

Open the sldvdemo\_flipflop example model.

```

open_system('sldvdemo_flipflop')

```

Using the default settings, run the test generation analysis on the example model.

```

[status, filenames] = sldvrun('sldvdemo_flipflop')

```

```

Checking compatibility for test generation: model 'sldvdemo_flipflop'

Compiling model...done

Building model representation...done

Generating tests using model representation from 14-Dec-2018 16:36:43...

....

Completed normally.

Generating output files:

Results generation completed.

Data file:

H:\work\sldv_output\sldvdemo_flipflop\sldvdemo_flipflop_sldvdata.mat

status =

1

```

Close the example model.

bdclose('sldvdemo\_flipflop')

Reopen the example model. Load analysis results for the model from the data file that the analysis generated.

```

sldvloadresults('sldvdemo_flipflop',filenames.DataFile)

ans =

1

```

You can view the loaded analysis results in the Simulink Design Verifier Results Summary window. To open the Results Summary window, on the **Design Verifier** tab, in the **Review Results** section, click **Results Summary**.

### **Input Arguments**

#### model - Name or handle of model

character vector | string scalar

Name of the model or handle of model for which to load analysis results.

```

Example: 'sldvdemo_cruise_control'

Example: 'sldvdemo_flipflop'

```

#### dataFile — Name of data file containing analysis results

character vector | string scalar

The name of the data file containing the analysis results. dataFile must contain analysis results for the specified model.

If dataFile is generated with a previous version of model, when you load the results from dataFile, you might see unexpected effects. To avoid inconsistencies between your model and the analysis results data, when you specify dataFile, choose a data file that contains results from the same version of the model.

For more information about analysis data files, see "Simulink Design Verifier Data Files".

```

Example: 'results.mat'

Example: 'sldv_output\sldvdemo_flipflop

\sldvdemo_flipflop_sldvdata.mat'

```

Example: 'sldv\_output\my\_model\my\_model\_sldvdata.mat'

### **Output Arguments**

#### status — Outcome of attempt to load results

logical

Outcome of attempt to load results, which returns as a logical value.

| Logical Value Returned | Status of Loaded Results       |  |

|------------------------|--------------------------------|--|

| true                   | Processing completed normally. |  |

| false                  | An error occurred.             |  |

### See Also

sldvhighlight|sldvreport

### **Topics**

"Review Analysis Results" "Simulink Design Verifier Data Files" Introduced in R2013b

# sldvlogsignals

Log simulation input port values

## Syntax

```

data = sldvlogsignals(model_block)

data = sldvlogsignals(harness_model)

data = sldvlogsignals(harness_model, test_case_index)

```

Note sldvlogsignals replaces sldvlogdata.

## Description

data = sldvlogsignals(model\_block) simulates the model that contains

model\_block and logs the input signals to the model\_block block. model\_block must

be a Simulink Model block. sldvlogsignals records the logged data in the structure

data.

data = sldvlogsignals(harness\_model) simulates every test case in the harness\_model and logs the input signals to the Test Unit block in the harness model. Generate harness\_model by using Simulink Design Verifier analysis, sldvmakeharness, or slvnvmakeharness.

data = sldvlogsignals(harness\_model, test\_case\_index) simulates every test case in the Signal Builder or Signal Editor block of the harness\_model that specifies the test\_case\_index. sldvlogsignals logs the input signals to the Test Unit block in the harness model. If you omit test\_case\_index, sldvlogsignals simulates every test case in the Signal Builder or Signal Editor.

## **Examples**

#### Create a Harness Model by Using Logged Signals

Use logged signals to create a harness model to visualize the data.

Simulate the CounterB Model block, which references the sldemo\_mdlref\_counter model, in the context of the sldemo\_mdlref\_basic model. Then log the data:

```

open_system('sldemo_mdlref_basic');

data = sldvlogsignals('sldemo_mdlref_basic/CounterB');

```

Create a harness model for sldemo\_mdlref\_counter model by using the logged data and the default harness options:

```

load_system('sldemo_mdlref_counter');

harnessOpts = sldvharnessopts;

[~, harnessFilePath] = ...

sldvmakeharness('sldemo_mdlref_counter', data, harnessOpts);

```

## **Input Arguments**

model\_block — Block path or handle to model

character vector | string scalar

Full block path name or handle to a Simulink Model block.

#### harness\_model - Name or handle to a harness model

character vector | string scalar

Name or handle to a harness model that the Simulink Design Verifier software, sldvmakeharness, or slvnvmakeharness creates.

#### test\_case\_index — Simulate test cases

character vector | cell array of character vectors | string array

Array of integers that specifies the test cases in the Signal Builder block of the harness model to simulate.

### **Output Arguments**

data — Structure of logged data structure

Structure that contains the logged data.

### See Also

sldvmakeharness | slvnvmakeharness

### **Topics**

"Extend Test Cases for Model with Temporal Logic" "Extend Test Cases for Closed-Loop System"

#### Introduced in R2010b

# sldvmakeharness

Generate harness model

### Syntax

```

[savedHarnessFilePath] = sldvmakeharness(model)

[savedHarnessFilePath] = sldvmakeharness(model, dataFile)

[savedHarnessFilePath] = sldvmakeharness(model, dataFile,

harnessOpts)

```

## Description

[savedHarnessFilePath] = sldvmakeharness(model) generates a test harness from the model, which is a handle to a Simulink model or the model name. sldvmakeharness returns the path and file name of the generated harness model in savedHarnessFilePath. sldvmakeharness creates an empty harness model. The test harness includes one default test case that specifies the default values for all input signals.

[savedHarnessFilePath] = sldvmakeharness(model, dataFile) generates a

test harness from the data file dataFile.

```

[savedHarnessFilePath] = sldvmakeharness(model, dataFile,

harnessOpts) generates a test harness from model by using the dataFile and the

harnessOpts, which specifies the harness creation options. If the dataFile is not

available, requires '' for dataFile.

```

If the software generates a harness, it does not imply that your model is compatible with the Simulink Design Verifier software.

## **Examples**

#### **Create a Test Harness**

Create a test harness for the sldvdemo\_cruise\_control model by using the default options.

Open the sldvdemo\_cruise\_control model by using the default options and create a harness model:

```

open_system('sldvdemo_cruise_control');

harnessopts=sldvharnessopts();

[harnessfile] = sldvmakeharness('sldvdemo_cruise_control', '', harnessopts);

```

## **Input Arguments**

#### model - Name or handle of model

character vector | string scalar

Handle to a Simulink model or the model name.

#### dataFile — Name of sldvData file

' ' (default) | character vector | string scalar

Name of the sldvData file.

harness0pts — Configurations for sldvmakeharness

character vector | string scalar

A structure whose fields specify these configurations for sldvmakeharness, as listed in this table.

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| harnessFilePath | Specifies the file path for creating the<br>harness model. If an invalid path is<br>specified, sldvmakeharness does not save<br>the harness model, but it creates and opens<br>the harness model. If this option is not<br>specified, sldvmakeharness generates a<br>new harness model and saves it in the<br>MATLAB current folder.<br>Default: ''                                                                           |

| modelRefHarness | Generates the test harness model that<br>includes model in a Model block. When<br>false, the test harness model includes a<br>copy of model.<br>Default: true                                                                                                                                                                                                                                                                 |

| usedSignalsOnly | When true, the Signal Builder block in the<br>harness model has signals for only input<br>signals used in the model. model must be<br>compatible with the software to detect the<br>used input signals.<br>When the harnessSource parameter is set<br>to Signal Editor, the Signal Editor block<br>in the harness model consists of unused bus<br>signals in addition to the input signals in<br>the model.<br>Default: false |

| Field         | Description                                                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| harnessSource | When set to Signal Builder, Simulink<br>Design Verifier generates a harness model<br>with the Signal Builder block as the Inputs<br>block. |

|               | When set to Signal Editor, Simulink<br>Design Verifier generates a harness model<br>with the Signal Editor block as the Inputs<br>block.   |

|               | Default: Signal Builder                                                                                                                    |

**Note** To create a default harnessOpts object, use sldvharnessopts.

## **Output Arguments**

#### savedHarnessFilePath — File name of generated harness model

character vector

The path and file name of the generated harness model.

### Alternatives

sldvmakeharness creates a test harness model without analyzing the model. To analyze the model and create a test harness:

- **1** Open the model.

- 2 On the **Design Verifier** tab, in the **Prepare** section, from the drop-down menu for the mode settings, click **Settings**.

- 3 In the Configuration Parameters dialog box, on the **Design Verifier > Results** pane, in **Harness model options**, set the options that you want.

- 4 Click OK.

- **5** To perform test generation analysis, on the **Design Verifier** tab, in the **Mode** section, select **Test Generation**.

6 Click Generate Tests.

## See Also

sldvharnessopts | sldvmergeharness | sldvrun | slvnvharnessopts |

slvnvmakeharness | slvnvmergeharness

### **Topics**

"Simulink Design Verifier Harness Models" "Create Harness Model" "Generate Test Harness Model and Record Coverage Data"

#### Introduced in R2009b

## sldvmergeharness

Merge test cases and initializations into one harness model

**Note** sldvmergeharness replaces sldvharnessmerge.

### **Syntax**

status = sldvmergeharness(name, models, initialization\_commands)

### Description

status = sldvmergeharness(name, models, initialization\_commands)

collects the test data and initialization commands from each test harness model in

models. The function saves the data and initialization commands in name, which is a

handle to the new model.

If name does not exist, sldvmergeharness creates name as a copy of the first model in models. sldvmergeharness then merges the data from other models listed in models into this model. If you create name from a previous sldvmergeharness run, subsequent runs of sldvmergeharness for name maintains the structure and initialization from the earlier run. If name matches an existing Simulink model, sldvmergeharness merges the test data from models into name.

sldvmergeharness assumes that name and the rest of the models in models have only one Signal Builder block on the top level. If a model in models has more than one Signal Builder block on the top level or its top-level Signal Builder block does not have the same number of signals as the top-level Signal Builder block in name, sldvmergeharness does not merge the model test data into name.

To combine the test cases that use different sets of parameter values, use sldvmergeharness with sldvgencov.

## Examples

#### Merge the Two Test Harnesses

Analyze the sldvdemo\_cruise\_control model for decision objectives and full coverage, and then merge the two test harnesses.

Open the sldvdemo\_cruise\_control example model.

```

model = 'sldvdemo_cruise_control';

open_system(model)

```

Set the sldvoptions and collect decision coverage.

```

opts1 = sldvoptions;

opts1.Mode = 'TestGeneration';

opts1.ModelCoverageObjectives = 'Decision';

opts1.HarnessModelFileName = 'first_harness';

opts1.SaveHarnessModel = 'on';

sldvrun(model, opts1);

```

Set the sldvoptions and collect full coverage.

```

opts2 = sldvoptions;

opts2.Mode = 'TestGeneration';

opts2.ModelCoverageObjectives = 'ConditionDecision';

opts2.HarnessModelFileName = 'second_harness';

opts2.SaveHarnessModel = 'on';

sldvrun(model, opts2);

```

Merge the two harness files.

```

status = sldvmergeharness('new_harness_model', {'first_harness',...

'second_harness'});

```

## **Input Arguments**

#### name - Name of new harness model

character vector | string scalar

Name of the new harness model, which is stored in the default MATLAB folder.

#### models — Names of harness models

character vector | cell array of character vectors | string array

A cell array that represents harness model names.

**initialization\_commands — Parameter settings for test cases** character vector | cell array of character vectors | string array

A cell array of the same length as models. initialization\_commands defines parameter settings for the test cases of each test harness model.

### **Output Arguments**

#### status — Status of merge harness

boolean

If the merge works, sldvmergeharness returns a status of 1. Otherwise, it returns 0.

### See Also

sldvgencov | sldvmakeharness | sldvrun

#### **Topics**

"Extend an Existing Test Suite" "Creating and Executing Test Cases" "Using Command Line Functions to Support Changing Parameters"

#### Introduced in R2010b

# sldvoptions

Create design verification options object

# Syntax

options = sldvoptions

options = sldvoptions(model)

# Description

**options** = **sldvoptions** returns an object **options** that contains the default values for the design verification parameters.

options = sldvoptions(model) returns the object options attached to model.

## **Examples**

#### **Create an Options Object**

Create an options object and set several parameters.

Create an opts option for the sldvdemo\_cruise\_control model:

```

opts = sldvoptions;

opts.AutomaticStubbing = 'on';

opts.Mode = 'TestGeneration';

opts.ModelCoverageObjectives = 'MCDC';

opts.ReportIncludeGraphics = 'on';

opts.SaveHarnessModel = 'off';

opts.SaveReport = 'off';

opts.TestSuiteOptimization = 'LongTestCases';

```

Get the options object for the sldvdemo\_cruise\_control model:

```

sldvdemo_cruise_control

optsModel = sldvoptions(bdroot);

```

optsCopy = optsModel.deepCopy; optsCopy.MaxProcessTime = 120;

## **Input Arguments**

model — Name or handle to a model

character vector | string scalar

Name or handle to a Simulink model.

### **Output Arguments**

#### options — Options for design verification

character vector

This table lists the parameters that comprise a Simulink Design Verifier options object.

| Parameter         | Description                                                                                                    | Values                                                         |

|-------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| AbsoluteTolerance | Specify an absolute value for tolerance in relational boundary tests.                                          | double {'1.0e-05'}                                             |

| Assertions        | Specify whether Assertion<br>blocks in your model are<br>enabled or disabled.                                  | 'EnableAll'<br>'DisableAll'<br>'UseLocalSettings'<br>(default) |

| AutomaticStubbing | Specify whether the software<br>ignores unsupported blocks and<br>functions and proceeds with the<br>analysis. | 'on' (default)<br>'off'                                        |

| Parameter                          | Description                                                                                                                                                                                                     | Values                                                                          |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| BlockReplacement                   | Specify whether the software<br>replaces blocks in a model<br>before its analysis.<br>When set to 'on', this<br>parameter enables<br>BlockReplacementModel-<br>FileName and<br>BlockReplacementRules-<br>List.  | 'on'<br>'off' (default)                                                         |

| BlockReplacementModel-<br>FileName | Specify a folder and file name<br>for the model that is the result<br>after applying block<br>replacement rules.<br>This parameter is enabled when<br>BlockReplacement is set to<br>'on'.                       | character array<br>'\$ <i>ModelName</i><br>\$_replacement' (default)            |

| BlockReplacementRules-<br>List     | Specify a list of block<br>replacement rules that execute<br>before its analysis.<br>This parameter is enabled when<br>BlockReplacement is set to<br>'on'.                                                      | character array<br>' <factorydefaultrules>'<br/>(default)</factorydefaultrules> |

| CodeAnalysisExtraOptions           | Extra options for analyzing S-<br>functions that have been<br>compiled to be compatible with<br>Simulink Design Verifier. See<br>"Support Limitations and<br>Considerations for S-Functions<br>and C/C++ Code". | character array<br>' ' (default)                                                |

| Parameter         | Description                                                                                                                                                                                                                                                      | Values                                                            |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| CoverageDataFile  | Specify a folder and file name<br>for the file that contains data<br>about satisfied coverage<br>objectives.                                                                                                                                                     | character array<br>' ' (default)                                  |

|                   | This parameter is enabled when IgnoreCovSatisfied is set to 'on'.                                                                                                                                                                                                |                                                                   |

| CovFilter         | For test generation and design<br>error detection analysis, specify<br>whether to ignore objectives<br>stored in coverage filter file.<br>When set to on, this parameter                                                                                         | 'on'<br>'off' (default)                                           |

| CovFilterFileName | enables CovFilterFileName.<br>For test generation and design<br>error detection analysis, specify<br>a name for the coverage filter<br>file that contains objectives to<br>exclude from analysis.<br>This parameter is enabled when<br>CovFilter is set to 'on'. | character array<br>' ' (default)                                  |

| DataFileName      | Specify a folder and file name<br>for the MAT-file that contains<br>the data generated during the<br>analysis, stored in an sldvData<br>structure.<br>This parameter is enabled when<br>SaveDataFile is set to 'on'.                                             | character array<br>'\$ <i>ModelName</i> \$_sldvdata'<br>(default) |

| DesignMinMaxCheck | Specify whether to check that<br>the intermediate and output<br>signals in your model are within<br>the range of specified minimum<br>and maximum constraints.                                                                                                   | 'on'<br>'off' (default)                                           |

| Parameter                     | Description                                                                                                                                                                              | Values                  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| DesignMinMaxConstraints       | Specify whether Simulink<br>Design Verifier software<br>generates test cases that<br>consider specified minimum and<br>maximum values as constraints<br>for input signals in your model. | 'on' (default)<br>'off' |

| DetectActiveLogic             | Specify whether to analyze your<br>model for active logic.<br>This parameter is enabled only<br>if DetectDeadLogic is set to<br>'on'.                                                    | 'on'<br>'off' (default) |

| DetectDeadLogic               | Specify whether to analyze your model for dead logic.                                                                                                                                    | 'on'<br>'off' (default) |

| DetectDivisionByZero          | Specify whether to analyze your model for division-by-zero errors.                                                                                                                       | 'on' (default)<br>'off' |

| DetectDSMAccessViolation<br>s | Specify whether to analyze your model for data store access violations.                                                                                                                  | 'on'<br>'off' (default) |

| DetectInfNaN                  | Specify whether to analyze your<br>model for non-finite and NaN<br>floating-point values.                                                                                                | 'on'<br>'off'(default)  |

| DetectInteger0verflow         | Specify whether to analyze your<br>model for integer and fixed-<br>point data overflow errors.                                                                                           | 'on' (default)<br>'off' |

| DetectOutOfBounds             | Specify whether to analyze your model for out of bounds array access errors.                                                                                                             | 'on' (default)<br>'off' |

| DetectSubnormal               | Specify whether to analyze your<br>model for subnormal floating-<br>point values.                                                                                                        | 'on'<br>'off'(default)  |

| Parameter                           | Description                                                                                                                                     | Values                           |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| DisplayReport                       | Display the report that the<br>Simulink Design Verifier<br>analysis generates after<br>completing its analysis.                                 | 'on' (default)<br>'off'          |

|                                     | This parameter is enabled when SaveReport is set to 'on'.                                                                                       |                                  |

| DisplayUnsatisfiable-<br>Objectives | Specify whether to display<br>warnings if the analysis detects<br>unsatisfiable test objectives.                                                | 'on'<br>'off' (default)          |

|                                     | This parameter is enabled when<br>Mode is set to<br>'TestGeneration'.                                                                           |                                  |

| ExistingTestFile                    | Specify a folder and file name<br>for the MAT-file that contains<br>the logged test case data.                                                  | character array<br>' ' (default) |

|                                     | This parameter is enabled when<br>Mode is set to<br>'TestGeneration' and<br>ExtendExistingTests is set<br>to 'on'.                              |                                  |

| ExtendExistingTests                 | Extend the Simulink Design<br>Verifier analysis by importing<br>test cases logged from a<br>harness model or a closed-loop<br>simulation model. | 'on'<br>'off' (default)          |

|                                     | When set to 'on', this<br>parameter enables<br>ExistingTestFile and<br>IgnoreExistTestSatisfied.                                                |                                  |

|                                     | This parameter is enabled when<br>Mode is set to<br>'TestGeneration'.                                                                           |                                  |

| Parameter                     | Description                                                                                                                                                                                                        | Values                                                           |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| HarnessModelFileName          | Specify a folder and file name<br>for the harness model.<br>This parameter is enabled when<br>SaveHarnessModel is set to<br>'on'.                                                                                  | character array<br>'\$ <i>ModelName</i> \$_harness'<br>(default) |

| HarnessSource                 | Specify the type of the Inputs<br>block for the harness model.<br>This parameter is enabled when<br>SaveHarnessModel is set to<br>'on'.                                                                            | 'Signal Builder'(default)<br>'Signal Editor'                     |

| IgnoreCovSatisfied            | Specify to analyze the model,<br>ignoring satisfied coverage<br>objectives, as specified in<br>CoverageDataFile.                                                                                                   | 'on'<br>'off' (default)                                          |

| IgnoreExistTestSatisfied      | Ignore the coverage objectives<br>satisfied by the logged test<br>cases in ExistingTestFile.<br>This parameter is enabled when<br>Mode is set to<br>'TestGeneration' and<br>ExtendExistingTests is set<br>to 'on'. | 'on' (default)<br>'off'                                          |

| IncludeRelationalBoundar<br>Y | Specify generation of test cases<br>that satisfy relational boundary<br>objectives.                                                                                                                                | 'on'<br>'off' (default)                                          |

| MakeOutputFilesUnique         | Specify whether the software<br>makes its output file names<br>unique by appending a numeric<br>suffix.                                                                                                            | 'on' (default)<br>'off'                                          |

| MaxProcessTime                | Specify the maximum time (in seconds) for analyzing a model.                                                                                                                                                       | double<br>'300' (default)                                        |

| Parameter        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Values                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| MaxTestCaseSteps | Specify the maximum number of<br>simulation steps when<br>attempting to satisfy a test<br>objective.                                                                                                                                                                                                                                                                                                                                                                                                                                 | int32<br>'10000' (default) |

|                  | The analysis uses the<br>MaxTestCaseSteps parameter<br>during certain parts of the test-<br>generation analysis to bound<br>the number of steps that test<br>generation uses. When you set a<br>small value for this parameter,<br>the parts of the analysis that are<br>bounded completes in less time.<br>When you set a larger value, the<br>bounded parts of the analysis<br>take longer, but it is possible for<br>these parts of the analysis to<br>generate longer test cases.<br>To achieve the best<br>performance, set the |                            |

|                  | MaxTestCaseSteps parameter<br>to a value large enough to<br>bound the longest required test<br>case, even if the test cases that<br>are ultimately generated are<br>longer than this value.                                                                                                                                                                                                                                                                                                                                          |                            |

|                  | When you set the<br>TestSuiteOptimization<br>parameter to<br>'LongTestCases', the<br>analysis uses successive passes<br>of test generation to extend a<br>potential test case so that it<br>satisfies more objectives. The<br>analysis applies the<br>MaxTestCaseSteps parameter                                                                                                                                                                                                                                                     |                            |

| Parameter               | Description                                                                                                                                                                                                                                                                                                                                                                                                                               | Values                                                                               |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                         | to each individual iteration of<br>test generation.<br>This parameter is enabled when<br>Mode is set to<br>'TestGeneration'.                                                                                                                                                                                                                                                                                                              |                                                                                      |

| MaxViolationSteps       | Specify the maximum number of<br>simulation steps over which the<br>software searches for property<br>violations.<br>This parameter is enabled<br>whenMode is set to<br>'PropertyProving' and<br>when ProvingStrategy is set<br>to 'FindViolation' or<br>'ProveWithViolation-<br>Detection'.                                                                                                                                              | int32<br>'20' (default)                                                              |